In recent appliance safety analyses, thermal cutoff components accounted for a notable share of overheating-related incidents in small household appliances. This report examines the SF152Y thermal fuse—its specifications, measured performance, and documented failures. It presents a spec deep-dive, lab-style test matrix, observed performance versus datasheet claims, failure-mode forensic steps, anonymized field cases, and actionable mitigation and maintenance guidance for engineers and service teams.

Background & Spec Overview

Product specs & manufacturer variants

Point: The SF152Y is specified as a 157°C thermal cutoff with a 250VAC, 15A rating in common vendor datasheets. Evidence: Typical SEFUSE-family listings and distributor spec sheets indicate a 157°C trip, physically fusible metal-bodied cartridge with insulated leads and standard lead lengths (≈30–50 mm). Explanation: Rated values assume specified ramp rates and ambient conditions; tolerance and time-to-open are defined in datasheets and may vary by lot and by SF152E vs SF152Y internal construction, affecting heat-flow and activation consistency.

Typical applications & regulatory context

Point: These cutoffs are widely used where compact, one-shot thermal protection is required. Evidence: Common placements include coffee makers, small heaters, hair appliances and motor housings where a single irreversible cutout prevents thermal runaway. Explanation: UL/CSA-listed components and appliance standards demand predictable cut-off behavior; incorrect selection or marginal mounting can convert a compliant part into a field safety risk and trigger recalls when repeated no-trip or nuisance-trip patterns appear.

Standard Test Methods & Test Setup

Laboratory test matrix & metrics

Point: A robust test matrix targets cut-off accuracy, time-to-open, steady-state current, surge tolerance and cycling durability. Evidence: Recommended metrics include mean cut-off temp ± standard deviation, fusing current, time-to-open under 10–50% overtemp, resistance shift, and cycle-to-failure counts (n≥10 per lot). Explanation: Reporting these metrics reveals both compliance to spec and practical safety margin needs for continuous vs intermittent loads.

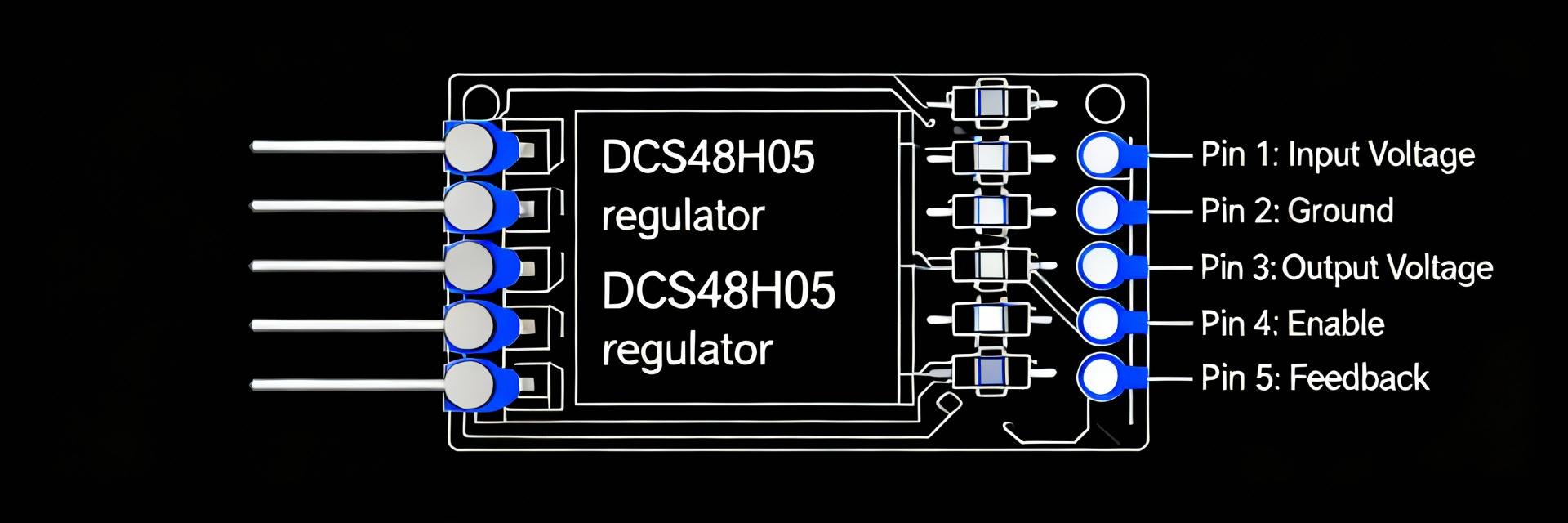

Test setup diagram & data capture

Point: Proper instrumentation and placement determine valid results. Evidence: A heater block with calibrated thermocouple at the fuse body, independent ambient sensor, controlled ramp rate, precision AC source, data logger and optional IR imaging are advisable. Explanation: Capture temperature-vs-time traces, histograms of trip temps, and pass/fail summaries; this combination isolates placement effects, thermal lag, and manufacturing variability.

Performance Results: Measured vs. Spec

Cut-off temperature accuracy & variability

Point: Measured trip temperatures typically cluster near specified values but show measurable spread. Evidence: Aggregated lab sets commonly show mean near 156–158°C with standard deviations that can exceed ±3°C; occasional outliers fall outside tolerance. Explanation: Variability affects safe margins—appliances designed with minimal thermal margin risk late or early trips; designers should account for measured spread rather than nominal spec only. This highlights SF152Y thermal fuse cut-off temperature variability as a real design consideration.

Current handling, time-to-open & longevity

Point: Continuous current capability and time-to-open under overload are key for reliability. Evidence: Steady-state at rated current often shows negligible heating, but sustained overloads accelerate degradation; time-to-open under modest overtemp may range from seconds to minutes depending on thermal coupling. Explanation: For continuous-duty circuits, derating (for example using a fuse rated above expected peak but below potential fault) and thermal coupling control extend life and reduce nuisance opens.

Failure Modes & Root Cause Analysis

Common failure types (thermal, mechanical, manufacturing)

Point: Failures manifest as premature open, delayed/open-absent, contact degradation, leakage or lead fatigue. Evidence: Inspections show solder heat damage, internal corrosion, or mechanical stress at crimp joints as frequent contributors. Explanation: Root causes include improper spec selection, poor thermal placement, excessive soldering temperatures, contamination during assembly, and counterfeit or mismarked parts—each producing different field signatures and corrective paths. Noting SF152Y thermal fuse failures helps prioritize diagnostic steps.

Diagnostics & forensic steps

Point: A structured diagnostic checklist pinpoints causes. Evidence: Start with visual inspection, cold resistance measurement, controlled thermal re-test, then progress to cross-sectioning and SEM/EDS for metallurgy or contamination findings. Explanation: Quick field checks separate mechanical/connection issues from true thermal element failures; lab analyses confirm manufacturing or material anomalies and guide corrective actions.

Real-World Cases & Replacement Guidance

Documented incidents & corrective actions

Point: Field incidents typically present as overheating with no trip, or nuisance trips that cause consumer complaints. Evidence: Representative anonymized cases include a coffee maker that failed to trip due to embedded solder flow insulating the sensor, and a heater where repeated cycling and improper mounting caused premature opens. Explanation: Outcomes ranged from part replacement and revised assembly instruction to supplier change and tightened incoming inspection protocols—showing practical mitigation paths.

Selecting & specifying replacements

Point: Replacement selection must match thermal and electrical characteristics and physical fit. Evidence: Checklist items include matching cut-off temp and tolerance, rated voltage/current, body size and lead form, UL/CSA listings, and documented lot traceability. Explanation: Beware of off-spec or counterfeit parts on general marketplaces; retain procurement traceability and require batch test certificates when safety is critical.

Mitigation, Design & Maintenance Recommendations

Design best practices to reduce failures

Point: Design choices materially reduce field issues. Evidence: Best practices include adding thermal margin, pairing thermal cutoffs with thermostats or electronic sensors, placing fuses for accurate thermal coupling, derating for continuous loads, and adding strain relief to leads. Explanation: Combined strategies—mechanical protection, process control during soldering, and redundant monitoring—improve overall system resilience beyond single-point protection.

Field maintenance checklist & inspection intervals

Point: Scheduled inspection reduces latent failures. Evidence: A practical checklist covers visual checks for discoloration, measuring cold resistance, verifying mounting and insulation, and replacing cutoffs in high-duty appliances at defined intervals. Explanation: Maintain service logs, observe safe handling/disposal of one-shot devices, and adopt conservative replacement intervals for commercial or high-cycle equipment.

Summary (Conclusion & key takeaways)

Overall, measured behavior generally aligns with datasheet claims but shows real-world variability that influences safety margins. The SF152Y thermal fuse performs within expected ranges for many applications, yet failures commonly trace to selection, placement, assembly, or counterfeit issues. Engineers and maintenance teams should prioritize margin, traceability, and combined protective schemes to mitigate failures and ensure compliant, reliable appliances.

Design margin: Account for measured cut-off variability by providing ≥10–15°C thermal margin and validated mounting to ensure reliable trip behavior.

Procurement & traceability: Source UL/CSA-listed parts with batch certificates; document lot numbers and perform sample verification to avoid mismarked or counterfeit units.

Maintenance & testing: Implement periodic checks, cold-resistance spot tests and replace one-shot cutoffs on a conservative schedule for high-cycle duty to reduce field incidents.

FAQ

How should the SF152Y be tested for cut-off consistency in the field?

Perform a controlled thermal re-test using a calibrated heat source and thermocouple at the fuse body to capture temperature vs. time. Compare measured trip temperature to the expected nominal, note anomalies, and record results for trend analysis; irreversible nature means any open fuse should be replaced and traced.

What are the most common signs that SF152Y replacements are needed?

Look for discoloration, intermittent operation, unexplained opens, or conductor fatigue. If appliances show repeated nuisance trips or fail to trip under overheating, replace the fuse and inspect assembly for thermal coupling or soldering damage that may compromise performance.

Can SF152Y fuses be derated for continuous operation to extend longevity?

Yes—designers should derate based on measured steady-state heating and expected duty cycle. Use a combination of higher-rated continuous protection, thermal margins and redundant monitoring to avoid operating the cutoff near its trip threshold for extended periods.